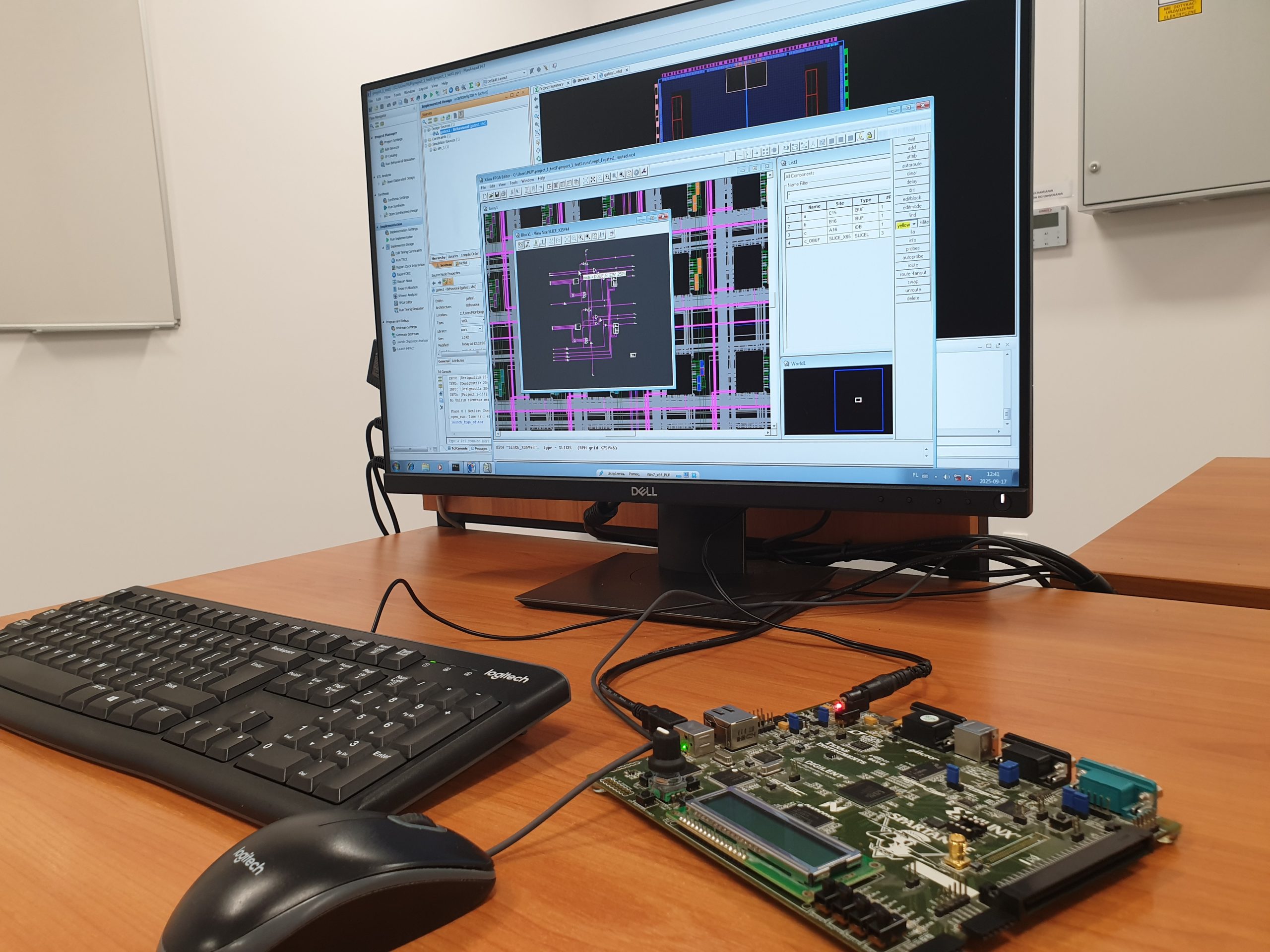

Pracowania Układów Programowalnych

Numer sali: 0.12

Lokalizacja: Centrum Nauk Technicznych przy ul. Wileńskiej 7, 87-100 Toruń

Kierunek studiów: Automatyka i Robotyka s1; Automatyka i Robotyka s2

Przedmiot w systemie USOS: 0800-UPROV, 0800-AR2SPOKO

Opiekun pracowni: dr Robert Frankowski

Dopuszcza się realizację wybranych tematów ćwiczeń w oparciu o zaproponowane przez Prowadzącego zajęcia zestawy laboratoryjne.

Tematy ćwiczeń:

-

Implementacja odbiornika PS2 w strukturze układu programowalnego Spartan 3E (PS2, Dekoder, VHDL, FPGA, Xilinx)

Celem ćwiczenia jest wykonanie odbiornika PS2 oraz zapoznanie się z zestawem laboratoryjnym firmy Xilinx/AMD Spartan 3E Starter Board . W celu wizualizacji odczytanych z portu PS2 danych posłuży dekoder którego wyjście podłączone jest pod diody LED płytki prototypowej. Źródłem przesyłanych informacji jest klawiatura PS2 podłączona do zestawu laboratoryjnego.

-

Projekt i implementacja liczników synchronicznych i asynchronicznych w strukturze układu programowalnego FPGA Spartan-6 (ATLYS, Schematic, Licznik synchroniczny i asynchroniczny, pamięć ROM)

Celem ćwiczenia jest implementacja projektu logicznego w strukturze układu programowalnego Spartan-6 przy pomocy programu narzędziowego firmy Xilinx – ISE Design Suite. Student powinien nabyć praktycznej wiedzy na temat funkcjonalnego oraz strukturalnego projektowania liczników synchronicznych i asynchronicznych, a także używanych narzędzi i metod stosowanych do wielopoziomowego opisu projektu. Pobierz

-

Projekt i implementacja nadajnika transmisji szeregowej w strukturze układu programowalnego FPGA Spartan2 (RS232, Spartan2, Maszyna stanów)

Nabycie umiejętności w programowaniu układu FPGA Spartan2 i zestawu laboratoryjnego DS-BD-2SLC przy pomocy narzędzia programistycznego ISE9.1, oraz wykorzystanie maszyny stanów do realizacji nadajnika transmisji szeregowej. Pobierz

-

Projekt i implementacja procesora PicoBlaze w strukturze Spartan-3E (Spartan-3E Starter Kit, PicoBlaze, KCPSM, pBlazIDE)

Nabycie umiejętności w posługiwaniu się oprogramowaniem ISE Design Siute. Zapoznanie się z zestawem prototypowym Spartan-3E FPGA Starter Kit, a następnie wykonanie projektu układu modulatora PWM ze zmiennym wypełnieniem okresu, stosując do tego celu procesor PicoBlaze. Pobierz

-

Implementacja bloków mnożących w strukturze FPGA typu VIRTEX-5 (GENESYS, Core Generator, DSP48E, HD44780, ST7066U)

Celem ćwiczenia jest zdobycie umiejętności wykorzystywania wbudowanych bloków funkcjonalnych w strukturach układów programowalnych FPGA typu Virtex-5, oraz posługiwania się narzędziem „Core Generator”. W ćwiczeniu należy wykonać projekt realizujący mnożenie dwóch liczb ze znakiem stosując do tego celu komponent DSP48E. Wynik mnożenia wyświetlony zostanie na wyświetlaczu LCD PC1602-D. Pobierz

-

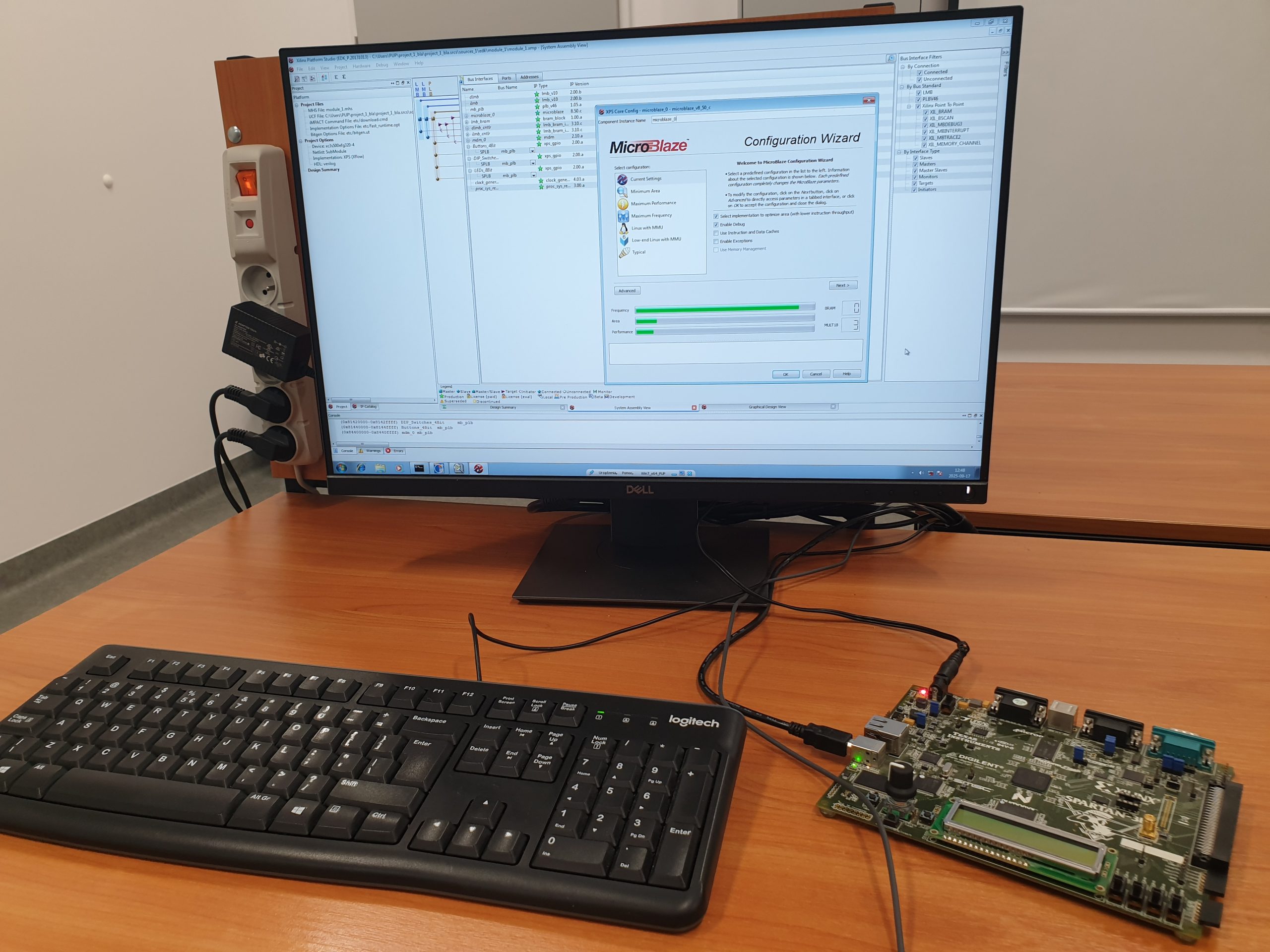

Implementacja wirtualnego procesora w strukturze FPGA typu SPARTAN-3 (Microblaze, EDK, XPS, wyświetlacz 7-segmentowy)

Celem ćwiczenia jest zdobycie umiejętności wykorzystywania narzędzia EDK ułatwiającego projektowanie wirtualnych procesorów wbudowanych w układy programowalne FPGA XILINX. W ćwiczeniu należy wykonać projekt czasomierza wyświetlającego kolejne wartości jednostek czasu na wyświetlaczu 7-segmentowym jako programu wykonującego się na procesorze Microblaze. Pobierz

-

Implementacja wbudowanych bloków funkcjonalnych DCM i PLL w strukturze programowalnej SPARTAN-6 (ATLYS, CMT, DCM, PLL, DLL, DFS, DDS, FPGA Editor)

Celem ćwiczenia jest zapoznanie się z zasobami logicznymi jakie oferuje układ programowalny typu FPGA Spartan-6 (XC6SLX45-CSG324C) a w szczególności poznanie wbudowanych bloków funkcjonalnych CMT (Clock Management Tiles) i oferowanych przez nie bloków DCM (Digital Clock Managers) oraz pętli PLL (Phase Locked Loop), stosowanych w procesie przetwarzania sygnałów zegarowych. Pobierz

-

Projekt i implementacja układu analogowo-cyfrowego w strukturach PsoC (asembler, DAC, ADC, LCD, RS232)

Zapoznanie się z budową i możliwościami układów analogowo-cyfrowych firmy Cypress, a w szczególności układem CY8C26643. Stworzenie projektu układu (opisanego w języku asembler) do pomiaru napięcia. Pobierz

-

Obsługa wyświetlacza LCD VI-201-DP-RC-S (wyświetlacze LCD, FPGA)

Zapoznanie się z obsługą narzędzia do syntezy i implementacji projektu, napisanego w języku VHDL, jakim jest ISE9.2. Zapoznanie się z budową i możliwościami płytki prototypowej z układem Spartan II XC2S100 na pokładzie. Stworzenie projektu pozwalającego na wyświetlenie wartości 4-bitowego licznika modulo 10. Pobierz

-

Projekt modulatora PWM w strukturze układu Virtex-II Pro (PWM, XC2VP4, 2VPxLC, licznik, dzielnik)

Ćwiczenie polega na zaprojektowaniu układu modulatora PWM ze zmiennym wypełnieniem okresu, dokonaniu jego implementacji do struktury programowalnej XC2VP4 oraz sprawdzeniu poprawności działania. Realizacja ćwiczenia umożliwi nabycie praktycznych umiejętności w posługiwaniu się narzędziem ChipScope-Pro do weryfikacji poprawności projektu bezpośrednio w strukturze FPGA. Pobierz

-

Wykorzystanie bloków pamięciowych RAMB w układach FPGA (RAMB, XC2V1000, V2MB1000, RAMB)

Celem ćwiczenia jest zapoznanie studenta z możliwościami bloków pamięciowych RAMB będących obecnie jednym z podstawowych zasobów układu programowalnego FPGA. W trakcie zajęć student zdobędzie praktyczną umiejętność konfiguracji, implementacji i wykorzystania w. w. bloków pamięciowych poprzez opis w języku VHDL. Pobierz

-

Opis i implementacja układu cyfrowego z wykorzystaniem Matlaba (System-Generator, Matlab, Virtex4, ML403)

Celem ćwiczenia jest zapoznanie studenta z narzędziem System-Generator oraz pokazanie możliwości wykorzystania Matlaba i Simulinka w opisie układów cyfrowych implementowanych w struktury FPGA. W trakcie tego ćwiczenia prosty projekt układu cyfrowego zostanie opisany w środowisku Matlab a następnie zaimplementowany do układu programowalnego. Student ma możliwość sprawdzić działanie projektu wykorzystując symulację oraz obserwując działający układ. Pobierz

Dodatkowe materiały niezbędne do realizacji powyższych ćwiczeń można

pobrać w tym miejscu: Pobierz.

Regulamin BHP obowiązujący na Pracowni Układów Programowalnych: Pobierz.

ul. Wileńska 7, 87-100 Toruń

ul. Wileńska 7, 87-100 Toruń